# RCA REVIEW

a technical journal

RADIO AND ELECTRONICS RESEARCH • ENGINEERING

Published quarterly by RCA LABORATORIES in cooperation with all subsidiaries and divisions of

**RADIO CORPORATION OF AMERICA**

| VOLUME XXIII                              | December 1962                                                               | NUMBER 4                      |

|-------------------------------------------|-----------------------------------------------------------------------------|-------------------------------|

|                                           | CONTENTS                                                                    |                               |

| An Analysis of the Eff<br>Tunnel-Diode Ba | ects of Reactances on the Perf<br>lanced-Pair Logic Circuit<br>J. J. GIBSON | PAGE<br>ormance of the<br>457 |

|                                           | nel-Diode Balanced-Pair Logic<br>S. MIILLER AND R. A. POWLUS                | •                             |

|                                           | eed Ferrite Memory<br>NELSON, R. LOCHINGER, AND J.                          |                               |

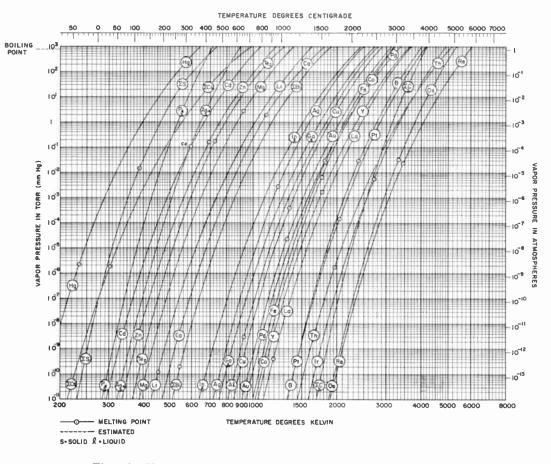

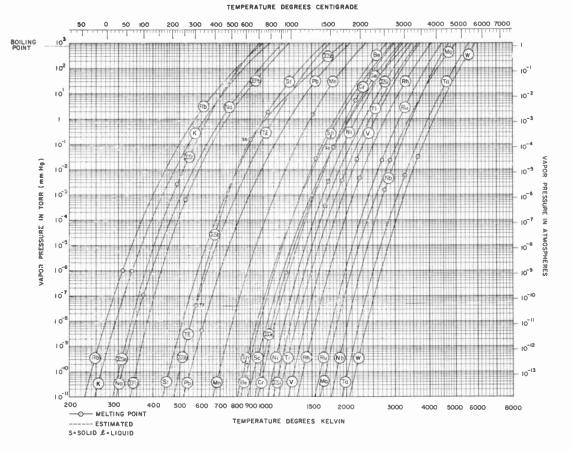

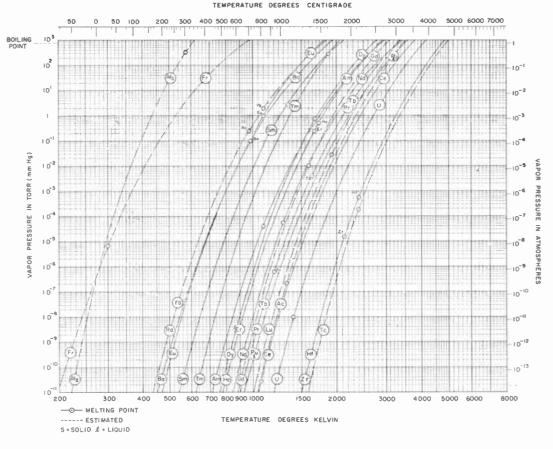

| Vapor Pressure Data f                     | or the Solid and Liquid Eleme<br>R. E. Honng                                | nts 567                       |

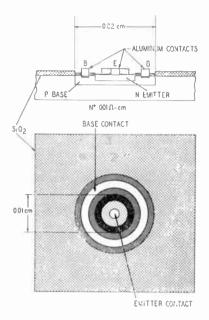

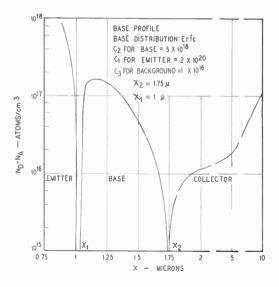

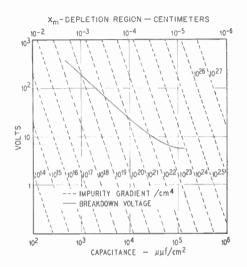

| sistors                                   | for Double-Diffused Silicon S<br>SEL, H. S. VELORIC, AND A. BI              | 587                           |

| RCA TECHNICAL PAPER                       | RS                                                                          | 617                           |

| AUTHORS                                   |                                                                             | 621                           |

| INDEX, VOLUME XXIII                       | (1962)                                                                      | 625                           |

© 1962 by Radio Corporation of America All rights reserved

**RCA REVIEW** is regularly abstracted and indexed by Abstracts of Photographic Science and Engineering Literature, Applied Science and Technology Index, Bulletin Signalétique des Télécommunications, Chemical Abstracts, Electronic and Radio Engineer, Mathematical Reviews, and Science Abstracts (I.E.E.-Brit.).

# RCA REVIEW

# **BOARD OF EDITORS**

Chairman R. S. Holmes RCA Laboratories

E. I. ANDERSON Home Instruments Division

> A. A. BARCO RCA Laboratories

G. L. BEERS Radio Corporation of America

G. H. BROWN Radio Corporation of America

> A. L. CONRAO RCA Service Company

E. W. ENGSTROM Radio Corporation of America

D. H. Ewing Radio Corporation of America

A. N. GOLDSMITH Honorary Vice President, RCA

> J. HILLIER RCA Laboratories

E. C. HUGHES Electron Tube Division

E. A. LAPORT Radio Corporation of America

> H. W. LEVERENZ RCA Laboratories

G. F. MAEDEL RCA Institutes, Inc.

W. C. MORRISON Defense Electronic Products

> L. S. NERGAARD RCA Laboratories

G. M. NIXON National Broadcasting Company

> H. F. OLSON RCA Laboratories

J. A. RAJCHMAN RCA Laboratories

D. S. RAU RCA Communications, Inc.

D. F. SCHMIT Radio Corporation of America

L. A. SHOTLIFF RCA International Division

S. STERNBERG Astro-Electronics Division

> W. M. WEBSTER RCA Laboratories

Secretary C. C. Foster RCA Laboratories

#### REPUBLICATION AND TRANSLATION

Original papers published herein may be referenced or abstracted without further authorization provided proper notation concerning authors and source is included. All rights of republication, including translation into foreign languages, are reserved by RCA Review. Requests for republication and translation privileges should be addressed to *The Manager*.

# AN ANALYSIS OF THE EFFECTS OF REACTANCES ON THE PERFORMANCE OF THE TUNNEL-DIODE BALANCED-PAIR LOGIC CIRCUIT\*

#### Βy

#### JAMES J. GIBSON

RCA Laboratories. Princeton, N. J.

Summary—The concept of wave scattering is used in an analysis of the balanced-pair circuit. Lead inductances and diode capacitances introduce a delay in the transmission path between the two diodes in the circuit. It is shown that this delay, and not the finite switching speed of the diodes, is the principal factor which limits the speed of the circuit. At the present state of device and circuit technology, the maximum repetition rate at which the circuit can operate reliably with a fan power of four and a sinusoidal clock source is 250 mc. An attempt to optimize the circuit parameters indicates that for a wide range of realistic reactances the optimum peak current is 5 to 15 milliampercs. At this peak current the impedance level is such as to represent a compromise between the speed-limiting effects of lead inductances and diode capacitances.

#### INTRODUCTION

HE TUNNEL-DIODE BALANCED-PAIR logic circuit is a one-port threshold gate synchronously driven by an a-c source.<sup>1,2</sup> Directionality of the flow of information in a system of these gates can be obtained by driving successive gates with successive phases of a three-phase a-c source. The repetition rate, f, and the stage delay, 1/(3f), are consequently determined by the fundamental frequency of the a-c source. Unavoidable reactances determine the highest frequency at which the circuit can operate reliably and with a sufficient logic gain to be useful in a system. The purpose of this paper is to analyze the reactive effects, to estimate the maximum frequency, and to synthesize the circuit for high-frequency operation.

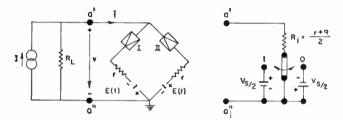

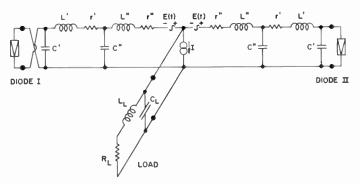

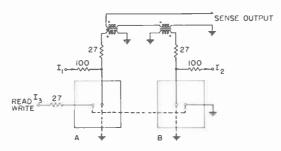

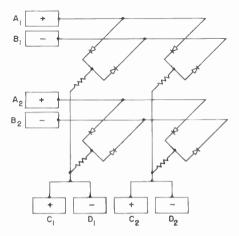

Figure 1 shows the circuit. It is a bridge consisting of two identical tunnel diodes and two identical resistors, r. A balanced d-c and a-c power source, represented by two identical equivalent voltage sources

<sup>\*</sup> Manuscript received April 17, 1962.

<sup>&</sup>lt;sup>1</sup> First suggested at the RCA Laboratories by Dr. Arthur Lo; French patent No. 1,246,084 January 27, 1960; Belgian patent No. 586,900 January 25, 1960.

<sup>&</sup>lt;sup>2</sup> E. Goto et al, "Esaki Diode High-Speed Logical Circuits," *I.R.E. Trans. on Electronic Computers*, EC-9, Vol. No. 1, p. 25, March (1960).

E(t) in series with the "source" resistors, r, drives the diodes in the same direction. The logic input signal and the threshold bias, represented by an equivalent current source, I, drive the diodes in opposite directions. The load is represented by an equivalent load resistor,  $R_L$ .

At the beginning of the a-c cycle both diodes are in their low-voltage positive-resistance regions and are driven towards their peaks and negative-resistance regions by the a-c power source. The logic input current favors one of the diodes, say diode I, with the consequence that diode I reaches its peak and negative-resistance region before diode II. As diode I goes over its peak, it sends an inhibiting signal to diode II, which, hopefully, reaches diode II in time and with sufficient strength to turn back diode II from its negative-resistance region, over its peak and into its low-voltage positive-resistance region. As diode I enters its negative-resistance region a regenerative process starts, switching diode I to its high-voltage positive-resistance region and

Fig. 1—The balanced-pair circuit and a crude "equivalent" toggle-switch circuit.

driving diode II deeply back into its low-voltage positive-resistance region. As a result, a large output voltage, with the same sign as the small logic input current, is obtained across the load  $R_L$ . At a later instant in the a-c cycle, diode I is reset to its low-voltage positive-resistance region, and the process can start over again.

The critical part of the process is the "locking" process which occurs during the small fraction of the a-c cycle when the diodes go over their peaks. The success of the locking process at high source rates, dE(t)/dt, depends on the intensity and the speed with which the diodes can communicate with each other over the lossy reactive network made up by the source resistors, the load, and unavoidable reactances. Reactive effects may also cause the circuit to burst into relaxation oscillations, even if the locking process is initially successful. In the subsequent analysis the diodes are considered as "individuals" which communicate with each other by emitting waves which are delayed and scattered by the circuit elements. Before proceeding to this analysis, which is the main topic of the paper, the performance of the circuit at low frequencies is reviewed. The constraints on the waveform E(t), on the available logic input, and on the required logic output, when the circuit is embedded in a practical system of similar gates, are also discussed. These system constraints are of great importance in a realistic estimate of the speed of the circuit.

# SOME DESIGN CONSIDERATIONS

Consider a specific example. The tunnel diodes have peak currents  $I_p = 10$  milliamperes, the series combination of the resistance of the tunnel-diode bulk material and the external source resistor is r = 6.5 ohms, and the load has a resistance  $R_L = 50$  ohms. A tunnel diode has

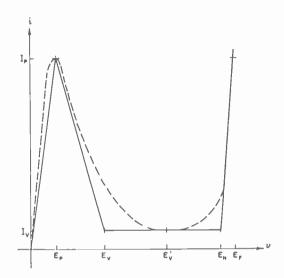

Fig. 2—Current versus voltage characteristic of germanium tunnel-diode with zero bulk resistance.

a current-versus-junction-voltage characteristic as shown in Figure 2. This characteristic is idealized in that the low- and high-voltage positive-resistance regions are linearized to have the same resistance, R = 3.5 ohms, over large portions of the characteristic. Some parameters specifying the characteristic are defined in Figure 2.

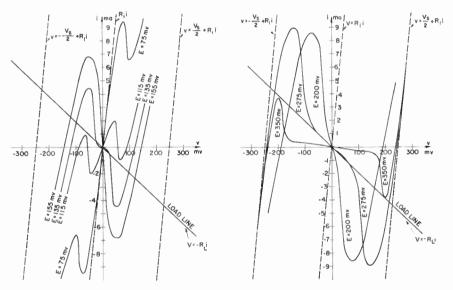

The current-versus-voltage characteristics seen by the load for various levels of the power source voltage, E, are shown in Figure 3. The load line for a very small logic input current is also shown in Figure 3. The dotted lines in Figure 3 are the nominal end states of

RCA REVIEW

the circuit, i.e., one nominal inactive state when both diodes are low, and two nominal active states when one diode is high and the other low. The nominal end states are defined in the crude equivalent "toggleswitch" circuit shown in Figure 1.

At the beginning of the process E is small and the operating point is close to the origin in Figure 3a. Seen from the load, the circuit in this state is equivalent to a resistance  $R_i = (r+R)/2 = 5$  ohms. As E increases, the diodes are driven towards their peaks, and the resist-

ance of the circuit seen by the load increases and becomes infinite at a source voltage

$$E_{\rm lock} = rI_p + V_p = 135 \text{ mv.}$$

(1)

At a slightly larger source voltage, the resistance seen by the load becomes negative and the circuit becomes unstable. At this point a number of events may occur which cannot be predicted from the characteristics in Figure 3. If everything functions as intended, the circuit switches to a stable state, producing a positive or negative output voltage depending on the sign of the logic input current. Once "locked" in one of these states, the circuit is insensitive to variations in the input and the logic input current can be removed. As *E* continues to increase, the operating point approaches one of the active end states as shown in Figure 3b. The output voltage and the output current approach the nominal values

$$|V_0| = \frac{R_L}{R_i + R_L} \frac{V_s}{2} = 225 \text{ mv},$$

$$|I_0| = \frac{1}{R_L + R_i} \frac{V_s}{2} = 4.5 \text{ ma}.$$

(2)

If E is increased beyond a certain maximum voltage,

$$E_{\max} = E_{\text{lock}} + \frac{R_L}{R_i + R_L} \left(\frac{V_F - V_p}{2}\right) = 344 \text{ mv},$$

(3)

both diodes are pulled over their peaks and the operating point switches back to a conditionally stable point at the origin. Under normal operation E must not exceed  $E_{\rm max}$ . As E decreases, the operating point moves back towards the origin. At a certain voltage  $E_{\rm min} = 115$  millivolts, which is less than  $E_{\rm lock}$ , the operating point becomes unstable and jumps back to the origin. This terminates the process.

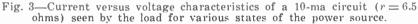

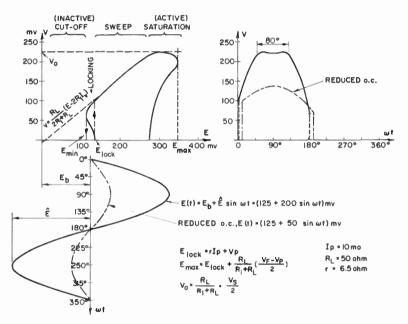

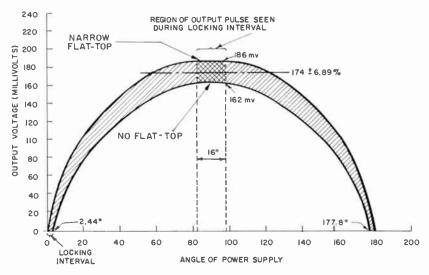

The intersections between the load line and the i-v characteristics in Figure 3 give a relation between the output voltage, v, and the source voltage, E. The mushroom-shaped characteristic in Figure 4 shows this relation. Given a waveform E(t) and assuming no reactances in the circuit, the output voltage as a function at time can be determined graphically. This is illustrated with an example in Figure 4.

The success of the locking process depends strongly on the source rate, dE/dt, during locking. If the source rate is too high, both diodes switch before they have time to "notice" each other. Although it is theoretically possible to synthesize a waveform E(t) which varies slowly during the locking process, it is difficult in practice to produce and distribute any waveform other than a combination of d-c and sinusoidal a-c. In a three-phase system of gates with reasonable tolerances on timing and lead lengths of interconnections, it is required<sup>3</sup> that the output pulse be approximately half a cycle wide at the base and have the widest possible flat top. Figure 4 shows that to meet these requirements the d-c bias must be approximately  $E_{lock}$ , and the a-c amplitude must be approximately

<sup>&</sup>lt;sup>3</sup> H. S. Miiller and R. A. Powlus, "An Evaluation of Tunnel-Diode Balanced-Pair Logic Systems," RCA Review, Vol. XXIII, p. 489, Dec. 1962.

RCA REVIEW

December 1962

$$\hat{E} \simeq E_{\max} - E_{\text{lock}} \simeq \frac{R_L}{R_i + R_L} \left( \frac{V_F - V_p}{2} \right). \tag{4}$$

In general  $R_i$  is substantially smaller than  $R_L$ , with the consequence that the required a-c amplitude is essentially independent of all circuit parameters; it is approximately 200 millivolts for germanium tunnel

Fig. 4—Output voltage as a function of source voltage and as a function of time.

diodes. With these constraints on E(t), the locking process unfortunately occurs when the source rate has a maximum

$$\frac{dE(t)}{dt} \bigg|_{E_{\text{lock}}} \approx 2\pi f \hat{E}.$$

(5)

This relation between the source rate during locking and the frequency is used later for an estimate of the maximum frequency. The source rate can be reduced by reducing the a-c amplitude, but this has the undesirable effect of reducing the amplitude of the output pulse and of rounding the pulse top as shown in Figure 4.

Although it is desirable to draw as much output current as possible from the circuit (theoretically, it is possible to draw a current

# ANALYSIS OF THE EFFECTS OF REACTANCES

$I_p - I_r \simeq 0.9 I_p$ ), a heavy load reduces  $E_{\max}$  and consequently also the width of the flat pulse top. To obtain flat-top pulses of nominal amplitude, the largest current that can be drawn from the circuit is between 0.4  $I_p$  and 0.6  $I_p$ . Thus, the load resistance  $R_L$  is established within narrow bounds.

The source resistance has a significant influence on the locking process. If r is too large the diodes may not be able to "communicate" with each other with sufficient intensity, with the consequence that both diodes switch. If r is too small the circuit may burst into oscillations. The source resistance also has a significant influence on the pulse shape. If r is increased, the saturation region of the v-E characteristic is increased, which has the desirable effect of widening the flat top of the output pulse. Another important consideration in the choice of r is "systems-noise." In a system, signals are generated by a large number of gates. To prevent these signals from propagating through the system to places where they are not desired, it is important to keep the internal impedance, and consequently r, small.

If all reactances are neglected, the choice of peak current determines only the level of the signals. It is obvious that if all resistances are scaled in inverse proportion to the peak current, the v-E characteristic, and consequently the performance of the circuit, is independent of peak current. Reactive effects, however, have a strong influence on the choice of peak current.

A detailed analysis is required to find an optimum design compromise among fan power, pulse shape, noise, and tolerance requirements on components, sources, and lead lengths of interconnections; such an analysis has been made.<sup>3</sup> The systems constraints are illustrated with only rough figures applicable to the typical circuit used here.

With a source voltage  $E(t) = 125 + 200 \sin \omega t$  millivolts, output pulses one half cycle wide at the base and with fairly wide flat tops of nominal amplitude are obtained, as shown in Figure 4. The output current is 0.4  $I_p$ . With a fan-in of two and a fan-out of two, the logic input current is 0.1125  $I_p$ . The interconnecting resistors, one in each of the four fan branches, are  $R_c = 4R_L - R_i = 195$  ohms, and the voltage attenuation of a signal propagating from a gate to one of its four neighbors is  $R_c/R_i = 39$ , which is adequate<sup>3</sup> to keep system noise at a tolerable level. With quite tight tolerances on components and sources, it has been estimated<sup>3</sup> that noise, internal imbalances, and input signal fluctuations reduce the effective available logic input current from .1125  $I_p$  to 0.0425  $I_p$ . Keeping in mind the constraints on E(t), on available logic input, and on required output, we can now consider the reactive effects.

#### RCA REVIEW

### THE REACTANCES

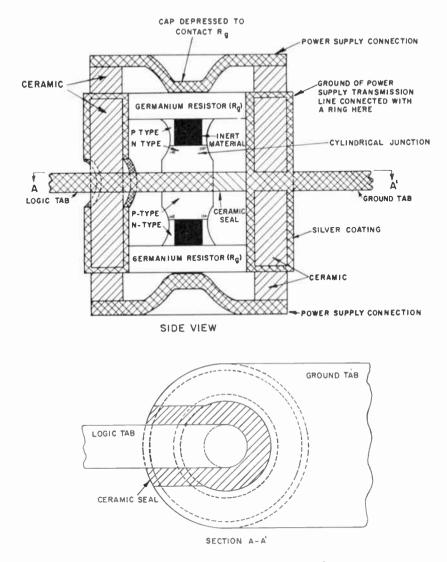

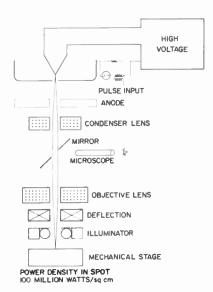

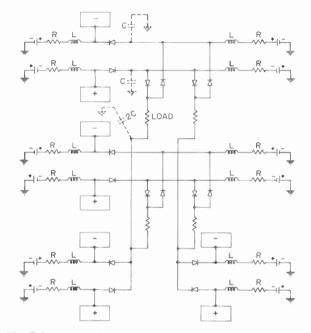

Figure 5 shows the circuit with reactances. The diodes in Figure 5 are "ideal" diodes, stripped of bulk resistance and reactances, having current-versus-voltage characteristics as shown in Figure 2. It can be seen from Figure 5 that a signal traveling from one diode to the other

Fig. 5-The balanced-pair circuit with reactances.

encounters many obstacles en route. These are

r' = bulk resistance of the diode,

r'' = external source resistance,

$R_L =$ load resistance,

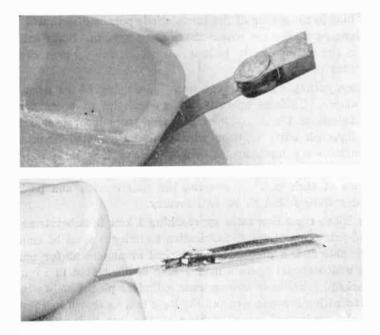

C' = nonlinear transition and injection capacitance of a tunnel diode. For diodes with peak currents ranging from 5 to 50 milliamperes, C' ranges from 0.5 to 12 pf for voltages below the valley voltage (pf = picofarad = 10<sup>-12</sup> farad). For higher voltages, C' increases rapidly with voltage. Usually C' is specified at the valley voltage. If C'<sub>v</sub> is the capacitance at the valley voltage, V<sub>v</sub> millivolts, then it is assumed that the capacitance at the peak voltage, V<sub>p</sub> millivolts, is

$$C'_{p} = C'_{v} \sqrt{\frac{580 \cdot V_{v}}{580 \cdot V_{p}}} \simeq \frac{1}{1.6} C'_{v}$$

C'' =case capacitance of a diode (0.5 to 1.5 pf),

$C_L = \text{stray capacitance of the load (0.5 to 1.5 pf)},$

L' = inductance of a diode (100 to 700 ph), (ph = picohenry = 10<sup>-12</sup> henry) L'' = inductance of a source resistor (100 to 700 ph),

$L_L =$  inductance of the load (> 500 ph).

Mutual inductances between  $L'_1$ ,  $L'_2$ ,  $L''_1$ , and  $L''_2$  can, for all practical purposes, be represented by equivalent changes in these inductances and in the load inductance,  $L_L$ .

Since the circuit in Figure 5 is too complicated for a practical analysis, the following simplifying approximations are made:

(1) The bulk resistance r' is incorporated with the external source resistance r'' to form an effective source resistance r = r' + r''. This is justified by the fact that the time constant r'C'' is much smaller than other time constants in the circuit.

(2) The stray capacitance of the load,  $C_L$ , is uniformly distributed along the load inductance to form a transmission line of characteristic impedance  $Z_L = \sqrt{L_L/C_L}$  and delay  $\tau_L = \sqrt{L_LC_L}$ . This is justified so long as the waveforms entering the load terminal have rise times greater than  $\tau_L$ .

(3) The junction capacitance C' is assumed to be constant and equal to the junction capacitance at peak voltage  $C'_p$ . This is justified for an analysis of the locking process, since both diodes operate in the vicinity of their peaks during locking.

(4) The capacitance C = C' + C'' is uniformly distributed along the inductance L = L' + L'' to form a transmission line of characteristic impedance  $Z = \sqrt{L/C}$  and delay  $\tau = \sqrt{LC}$ . This is a major approximation which we shall try to justify as we go along with the discussion.

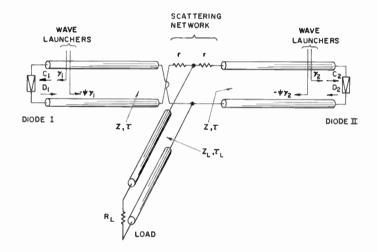

With these approximations the circuit takes the form of the transmission-line model shown in Figure 6. To get a feel for the magnitude of the characteristic impedances and the delays involved in this circuit, it will be assumed that the typical 10-milliampere circuit has the following reactances: C' = 1 pf, C'' = 1 pf,  $C_L = 0.4$  pf, L' = 200 ph, L'' = 200 ph,  $L_L = 1000$  ph, whereby C = 2 pf and L = 400 ph, and consequently Z = 14.14 ohms,  $\tau = 28.28$  ps,  $Z_L = 50$  ohms,  $\tau_L = 20$  ps (ps = picosecond =  $10^{-12}$  second). For all realistic assumptions about the reactances, Z varies between 4 and 40 ohms and  $\tau$  between 12 and 120 ps.

In the transmission-line model it is convenient to consider all signals as waves. The intensity of a wave at a particular instant and location can be defined as the square root of its instantaneous power. The signal at a diode port can thus be expressed by

$$C = \frac{1}{2} \left( \frac{v_D}{\sqrt{Z}} + i_D \sqrt{Z} \right) = \text{ incident wave on the diode in (watts)}^{\frac{1}{2}},$$

(7)

$$D = \frac{1}{2} \left( \frac{v_D}{\sqrt{Z}} - i_D \sqrt{Z} \right) = \text{reflected wave from the diode in (watts)}^{4},$$

(8)

where  $v_D$  is the voltage across the diode in volts, and  $i_D$  the current through the diode in amperes. Given a characteristic impedance Z and the  $i_D$ -versus- $v_D$  characteristic of the diode, the reflection properties

Fig. 6-The transmission line model of the balanced-pair circuit.

of the diode can be represented by a relation.

$$D = \theta(C) = \phi(C) + \psi C, \tag{9}$$

where  $\psi = (R - Z) / (R + Z)$  = reflection coefficient of the diode in the linear part of the low-voltage positive-resistance region, and  $\phi(C)$  = nonlinear part of the reflection characteristic  $\theta(C)$ .

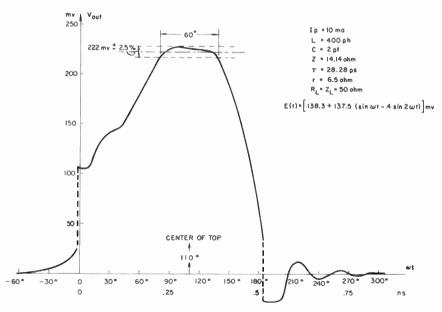

The reflection characteristic,  $D = \theta(C)$ , is the normalized tunneldiode characteristic  $i_D \sqrt{Z}$  versus  $v_D / \sqrt{Z}$  inverted and rotated 45° clockwise, as shown for three cases of peak currents and characteristic impedances in Figure 7. The nonlinear part  $\phi(C)$  of the reflection characteristic is shown for one of the cases in Figure 8. Figure 7

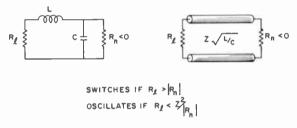

Fig. 7-Reflection characteristics of tunnel diodes.

Fig. 8—Nonlinear part of the reflection characteristic of a 10-ma diode with Z = 14.14 ohm.

shows that when the peak current and/or the characteristic impedance is large, the reflection characteristic exhibits hysteresis. Hysteresis indicates that whenever the diode is driven to a point in the negativeresistance region where the magnitude of the negative resistance,  $|R_n|$ , is equal to the characteristic impedance Z of the transmission line connected to the diode, the diode switches infinitely fast along a line C = constant. This means that the region of the characteristic where  $|R_n| < Z$  cannot be reached under any circumstances. The property of hysteresis is related in a simple manner to the stability conditions of a voltage-controlled negative-resistance device loaded by a resistor. These stability conditions are indicated in Figure 9. It is seen that whenever  $|R_n| < Z$  the system is unconditionally unstable. It is of interest for a justification of the transmission-line model that the stability conditions are the same whether all shunt capacitances are

Fig. 9-Stability conditions for a voltage controlled negative resistance.

lumped together at the negative-resistance element or are uniformly distributed along the lead inductance. It should be pointed out that although the stability criteria and the nature of the events which happen in an unstable state are the same for both models, the shapes of the waveforms generated in an unstable state are different. Infinitely fast switching, for example, can obviously not occur in a system with lumped reactances.

In the transmission line model shown in Figure 6, all the sources in the system are represented by equivalent "wave launchers" at the diode ports. This is permissible because of the assumption that the network which interconnects the ideal diodes is linear. To determine the intensity of the wave launchers, let the diodes be replaced by resistances R and let the currents through these resistances be  $i(t) + \Delta i$ and  $i(t) - \Delta i$ , where  $2 \Delta i$  is the logic input current and i(t) is caused by the power source E(t). If the reactances are small, the current i(t)is approximately ANALYSIS OF THE EFFECTS OF REACTANCES

$$i(t) = \frac{E(t)}{R+r}.$$

(10)

According to Equation (7) the incident wave on a resistor R caused by its closest launcher is

$$\gamma(t) \pm \Delta \gamma = \frac{1}{2} (i(t) \pm \Delta i) \left( \frac{R}{\sqrt{Z}} + \sqrt{Z} \right), \qquad (11)$$

which causes a reflected wave  $\psi(\gamma(t) \pm \Delta \gamma)$  where

$$\psi = \frac{R-Z}{R+Z} \,. \tag{12}$$

Consequently all the sources in the system can be replaced by a set of wave launchers  $\gamma(t) \pm \Delta \gamma$  directed towards the diodes, and a set of wave launchers  $-\psi(\gamma(t) \pm \Delta \gamma)$  directed from the diodes towards the network. The latter cancel the reflected waves from the diode ports when the diodes are replaced by resistances R, thus de-energizing the network which interconnects the resistances R. Consequently, all events which occur in the interconnecting network when the diodes are reinserted, can be attributed to the fact that the diodes depart from being linear resistances.

The events in the system can now be formally expressed. As a simplification, a load resistance  $R_L$  is chosen which matches the characteristic impedance,  $Z_L$ , of the load port. With this assumption, the incident waves on the diodes at time t are

$$\begin{pmatrix} C_{1}(t) \\ C_{2}(t) \end{pmatrix} = \begin{pmatrix} \gamma(t) + \Delta \gamma \\ \gamma(t) - \Delta \gamma \end{pmatrix} + \begin{pmatrix} S_{11} - S_{12} \\ -S_{12} - S_{11} \end{pmatrix} \begin{pmatrix} \theta [C_{1}(t - 2\tau)] - [\gamma(t - 2\tau) + \Delta \gamma] \psi \\ \theta [C_{2}(t - 2\tau)] - [\gamma(t - 2\tau) - \Delta \gamma] \psi \end{pmatrix},$$

$$(13)$$

where  $S_{11}$  is the reflection coefficient and  $S_{12}$  the transmission coefficient of the resistive pad made up by the source resistors and the load:

$$S_{11} = rac{r^2 - Z^2 + 2rZ_L}{(r+Z)(r+Z+2Z_L)}$$

$$S_{12} = \frac{2ZZ_L}{(r+Z)(r+Z+2Z_L)} \,. \tag{14}$$

The problem is to find the steady-state solution of Equation (13) for periodic sources  $\gamma(t)$ . However, it is much simpler to find the transient solution assuming that at the beginning of the process the system has recovered from past transients and that the diodes are on the linear parts of their low-voltage positive-resistance regions going towards their peaks under the influence of the wave launchers  $\gamma(t) \pm \gamma(t)$  $\Delta \gamma$ . If the reflection characteristic  $\theta(C)$  has no hysteresis, the sequence of events can be completely determined by iteration of Equation (13), given a starting point. If  $\theta(C)$  has hysteresis, several starting points must be tested to see where they lead. The iteration process is fairly simple, and some results of such point-by-point calculations are given later. A point-by-point calculation is fine for a final analysis of a given circuit operating under given circumstances. However, to estimate the maximum frequency,  $f_{max}$ , and to synthesize the circuit for highfrequency operation, an approximate explicit expression for  $f_{max}$  is required.

#### LOCKING

The events during locking can be discussed with the help of the simple circuit shown in Figure 6. At the beginning of the cycle, both diodes are low and both are driven towards their peaks by time-varying sources. Let the intensity  $\gamma(t) + \Delta \gamma$  of the wave launcher associated with diode I be ahead of the intensity  $\gamma(t) - \Delta \gamma$  of the wave launcher associated with diode II by a small amount,  $2\Delta\gamma$ , determined by the input logic signal. As long as the diodes are on the linear parts of their low-voltage positive-resistance regions, they behave as resistors R, and consequently nothing happens in the network which interconnects them, provided the circuit has recovered from past transients. There is no communication between the diodes and neither one of them knows which is ahead. As diode I enters the nonlinear region around its peak, it sends an inhibiting signal to diode II. This signal is delayed a time  $2\tau$  and attenuated by a factor  $S_{12}$  before it reaches diode II. In the meantime, diode II enters its nonlinear region. If the source rate  $d\gamma(t)/dt = \dot{\gamma}$  is high, diode II may go far into its negativeresistance region before it receives a significant inhibiting signal from diode I. If diode II goes far enough, a regenerative process starts which carries it over the negative-resistance region. After this regenerative process has terminated, it is possible, but not certain, that the inhibiting signal from diode I will reset diode II to a low state.

However, while switching, diode II emits a strong signal, which also may reset diode I to its low state. Thus both diodes may, temporarily, be brought back into their low states, until diode I switches again. This type of relaxation oscillation continues until the source intensity  $\gamma(t)$ becomes so large that the diodes can no longer reset each other. These oscillations cause an output consisting of one or many short pulses. Although it is possible for the process to end with diode I high and diode II low, it is more likely to end with both diodes in their valleys. The outcome depends on the shape of the diode characteristics throughout the negative-resistance regions, slight imbalances, slight variations in logic input, and slight variations in the waveform of the power sources. For reliable operation, it is therefore necessary that diode II not go very far into the steep part of its negative-resistance region. Exactly how far it can go is an academic question, since it is exceedingly difficult to manufacture tunnel diodes with tight tolerances on the shape of the negative-resistance region. Furthermore, since the steep part of the negative-resistance region spans a voltage range which is fairly small compared to the total voltage range of the characteristic, the precise limit to which diode II can go is of no practical concern. In terms of the transmission-line model, the incident wave on diode II must not exceed a certain critical value  $C_{\rm fire}$ . For diodes with hysteresis,  $C_{\rm fire}$  is close to the point where the diode switches unconditionally to a high state. For diodes without hysteresis,  $C_{

m fire}$ corresponds to a state somewhere between the peak and the steepest part of the negative-resistance region.

Given  $C_{\text{fire}}$ , what is the largest possible source rate  $\dot{\gamma}$  during locking? Let  $t_0$  be the instant when diode II is turned back, i.e., when

$$\left. \frac{dC_2(t)}{dt} \right|_{t=t_0} = \dot{C}_2(t_0) = 0.$$

Assume that the source rate  $\dot{\gamma}$  is so high, and the curvature of the reflection characteristics in the vicinity of the peaks so sharp, that both diodes are still in the linear parts of their low-voltage positive-resistance regions at an instant  $t_0 - 4\tau$ . A consequence of this assumption is that the incident waves on the diodes at an instant  $t_0 - 2\tau$  are caused only by their own wave launchers,

$$C_{1}(t_{0}-2\tau) = \gamma_{1}(t_{0}-2\tau) = \gamma(t_{0}-2\tau) + \Delta\gamma,$$

$$C_{2}(t_{0}-2\tau) = \gamma_{2}(t_{0}-2\tau) = \gamma(t_{0}-2\tau) - \Delta\gamma.$$

The incident wave on diode II at the instant  $t_0$  is therefore, according to Equation (13),

$$C_2(t_0) = \gamma_2(t_0) + S_{11} \phi[\gamma_2(t_0 - 2\tau)] - S_{12} \phi[\gamma_1(t_0 - 2\tau)].$$

Since  $\phi(C)$  is a monotonically increasing function of C, as shown in Figure 8, it follows that if  $S_{11} > S_{12}$ ,  $C_2(t_0)$  can be negative only if  $\gamma_1 > \gamma_2$ . Thus, if  $S_{11} > S_{12}$ , the success of the locking process depends entirely on the magnitude of the logic input signal. Since this signal is small and unreliable, reliable operation requires that  $S_{12}$  be substantially larger than  $S_{11}$ . When this is the case and when the logic signal is small, the equation for  $C_2(t_0)$  can be approximated by replacing  $\gamma_2$  by  $\gamma_1$  in the second term on the right, i.e.,

$$C_2(t_0) \simeq \gamma_2(t_0) - (S_{12} - S_{11}) \phi [\gamma_1(t_0 - 2\tau)].$$

(15)

Since the source rate is approximately constant for a duration of  $2\tau$ , the condition  $\dot{C}_2(t_0) = 0$  gives the relation

$$\phi' [\gamma_1(t_0 - 2\tau)] = \frac{1}{S_{12} - S_{11}}.$$

(16)

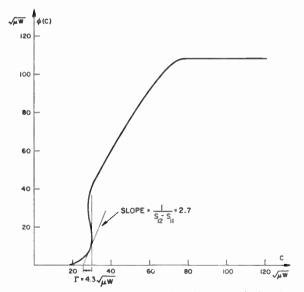

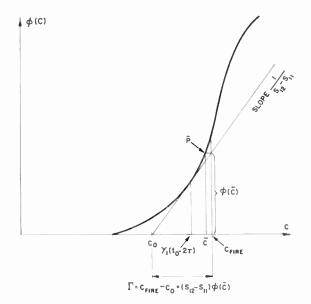

The graphical construction in Figure 10 shows that the tangent of the function  $\phi(C)$  with a slope  $1/(S_{12} - S_{11})$  intersects the C axis at

$$C_0 = \gamma_1 (t_0 - 2\tau) - (S_{12} - S_{11}) \phi [\gamma_1 (t_0 - 2\tau)].$$

(17)

Consequently, the condition  $C_2(t_0) \leq C_{\text{fire}}$  gives the relation

$$\gamma_2(t_0) - \gamma_1(t_0 - 2\tau) \simeq \dot{\gamma} 2\tau - 2\Delta \gamma \le C_{\text{fire}} - C_0 = \Gamma, \qquad (18)$$

or

$$\dot{\gamma} \leq \frac{1 + 2\Delta\gamma}{2\tau}, \tag{19}$$

where  $\Gamma$  is defined by the graphical construction in Figure 10.

Equation (19) can be expressed in terms of the circuit parameters. Figure 10 shows that  $\Gamma$  can be expressed as

$$\Gamma = (S_{12} - S_{11}) \phi (\overline{C}), \qquad (20)$$

where  $\overline{C}$  is close to, but less than,  $C_{\text{fire}}$ . According to Equations (7), (8), (9), and (14),

$$\Gamma = \frac{Z - r}{Z + r} \cdot \frac{\bar{v}_D - R\bar{\iota}_D}{\left(1 + \frac{R}{Z}\right)\sqrt{Z}}$$

(21)

where  $(\bar{v}_D, \bar{i}_D)$  is a point on the tunnel-diode characteristic corresponding to an incident wave  $\overline{C}$ . Thus  $(\bar{v}_D, \bar{i}_D)$  is somewhat closer to the peak than the point on the tunnel-diode characteristic corresponding to an incident wave  $C_{\text{fire}}$ , i.e., the point to which diode II is allowed to go.

Fig. 10—Graphical determination of the quantity  $\Gamma$  appearing in Equation (19).

If the source voltage E is a periodic function of time with a fundamental frequency f, the source rate during locking is

$$\frac{dE}{dt} \bigg|_{t=t_0} = 2\pi f \frac{dE(\vartheta)}{d\vartheta} \bigg|_{t=t_0}, \qquad (22)$$

where  $\vartheta = 2\pi ft$ . According to Equations (10), (11), and (22),

$$\dot{\gamma} = 2\pi f \frac{dE(\vartheta)}{d\vartheta} \left| \begin{array}{c} \left(1 + \frac{R}{Z}\right)\sqrt{Z} \\ \frac{1}{2(R+r)} \end{array} \right|, \quad (23)$$

RCA REVIEW

December 1962

$$2\Delta\gamma = \Delta i \left(1 + \frac{R}{Z}\right) \sqrt{Z}.$$

(24)

Insertion of Equations (21), (23), and (24) in Equation (19) gives an approximate expression for the maximum fundamental frequency of the a-c source;

$$f_{\max} \approx \frac{1}{2\pi \frac{dE\left(\vartheta\right)}{d\vartheta}} \left| \begin{array}{c} \cdot \frac{1}{\tau} \left[ \frac{\left(\bar{v}_{D} - R\bar{i}_{D}\right)\left(R + r\right)\left(Z - r\right)}{\left(1 + \frac{R}{Z}\right)^{2} Z\left(Z + r\right)} + \Delta i\left(r + R\right) \right] \right]$$

$$(25)$$

To illustrate this formula, consider the 10-milliampere circuit discussed earlier, for which r = 6.5 ohms, R = 3.5 ohms, Z = 14.14 ohms, and  $\tau = 28.28$  ps. The circuit operates with a sinusoidal a-c, as shown in Figure 4, for which

$$\left. rac{dE\left( artheta

ight) }{dartheta }

ight|_{t=t_{0}}=\hat{E}=200 \,\,\, {

m millivolts}.$$

A graphical determination of  $\Gamma$ , carried out in Figure 8, reveals that the factor  $\bar{v}_D - R\bar{i}_D$  is 56 millivolts. At the maximum frequency, diode II reaches the critical point of unconditional switching, which is where the negative resistance is equal to Z = 14.14 ohms. This is a little further than the point  $\bar{v}_D = 89$  millivolts,  $\bar{i}_D = 9.5$  milliamperes. Figure 2 indicates the location of this point. The effective logic input current, after all fluctuations are accounted for, is  $2\Delta i = .425$  milliampere, as estimated earlier. Insertion of these data in Equation (25) gives

$$f_{\rm max} = f_{\rm crit} + \Delta f = (255 + 60) = 315$$

megacycles. (26)

The first factor within the bracket of Equation (25) is independent of the input signal and contributes to  $f_{\rm erit}$ , while the second factor is proportioned to the input signal and contributes to  $\Delta f$ . To operate the circuit at a frequency larger than  $f_{\rm erit}$ , an input signal is required, while at frequencies below  $f_{\rm erit}$ , the circuit can operate with random positive and negative locking without input signal. Equation (26) indicates that even if the input signal is doubled, the maximum frequency increases only from 315 to 375 mc, i.e., 20 per cent. Thus, to

operate the circuit at frequencies substantially larger than  $f_{\rm crit}$ , a very large input signal is required, with the consequence that the logic gain becomes so small as to make the circuit useless.

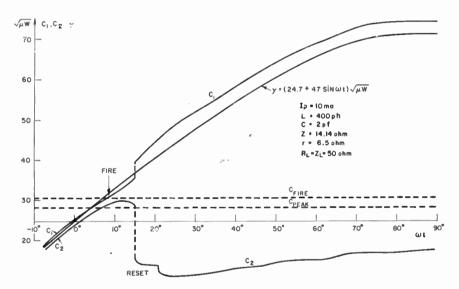

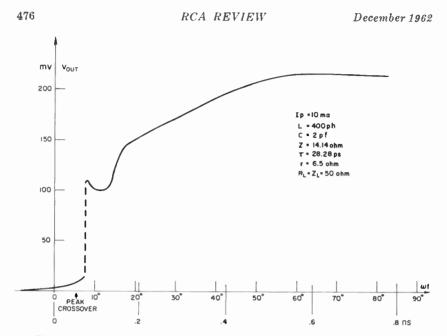

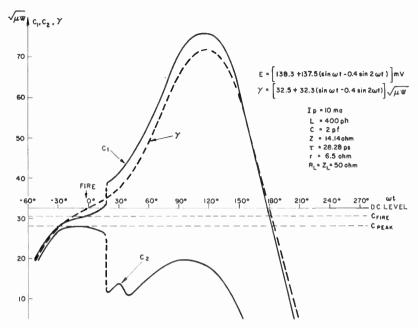

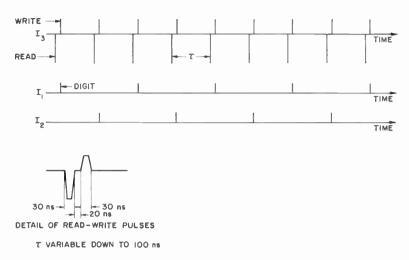

To check Equation (25), the sequence of events in the 10 milliampere circuit has been determined point by point by iteration of Equation (13). Figure 11 shows the incident waves on the diodes as a function of time when the circuit operates at 300 mc. It is seen that diode II is barely turned back before the incident wave reaches  $C_{\rm fire}$ . It is also seen that the success of the locking process is established before any fast regenerative process has started. The fact that the signals involved during locking are essentially made up of frequency components at substantially lower frequencies than the cutoff frequency

Fig. 11—Incident waves of the diodes in the 10-ma circuit operating with a 300-mc sinusoidal source.

of the actual reactive network, justifies the transmission-line model. Figure 12 shows the output pulse. It begins with a very slow rise during the locking process. The fact that the output during locking is very small justifies the approximation involved in neglecting reflections from the load due to a possible mismatch between  $R_L$  and  $Z_L$ . Since the diodes in this circuit have hysteresis, diode I switches infinitely fast, causing a sudden jump in the output. With some lumping of the distribution of the reactances, the rise-time of this "jump" will be of the order of magnitude of  $\tau$ . After the jump, the output hesitates

Fig. 12—Output pulse of the 10-ma circuit operating with a 300-mc sinusoidal source.

a little before it approaches a course which can be predicted by the static v-E characteristic in Figure 4.

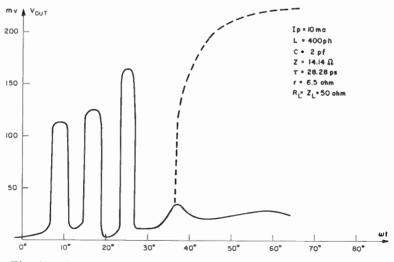

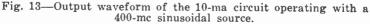

Figure 13 shows the output when the circuit runs at 400 mc. Both

# ANALYSIS OF THE EFFECTS OF REACTANCES

diodes switch, reset each other, switch again and then, depending on some very touchy conditions, either both diodes remain in their high states with no output (solid line), or diode II is reset with full output (dotted line). The short pulses in the output are typical for this mode of operation. To make the circuit work reliably at 400 mc, the input current must be increased by a factor of 2.4, i.e., to 1.02 milliamperes. In a system of gates with a fan power of four, this is about the maximum available logic input current, and there would be no margin for tolerances and noise. Point-by-point calculations by iteration of Equation (13) thus show that the circuit barely works at 300 mc, and that it does not work at 400 mc. This confirms the estimate of a maximum frequency of 315 mc indicated in Equation (26).

What can be done to increase the maximum frequency? Since not much can be done about the input signal, consideration is given to  $f_{\rm crit}$ , which depends on the first term within the bracket of Equation (25). For a given circuit, the only parameter that can be varied is the waveform of the source E(t). With a sinusoidal a-c, the amplitude of the a-c can be reduced to a point where the circuit barely locks and unlocks at the crests of the a-c, and theoretically there is no limit to the maximum frequency. However, the output pulse will be so poor that the circuit would be useless for operation in a system. Figure 4 shows the degradation of the pulse shape in the 10-milliampere circuit when the a-c is reduced by a factor of 4, i.e., from 200 to 50 millivolts, thereby theoretically boosting the maximum frequency from 315 to 1260 mc. Experimentally, balanced pair circuits have operated<sup>3</sup> with reduced a-c at frequencies above 1000 mc.

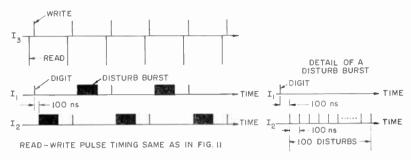

Another possible way of reducing the source rate during locking is to include harmonics in the a-c source. Figures 14 and 15 show that the 10-milliampere circuit can operate at 1000 mc when the a-c waveform contains 40 per cent second harmonic. The source rate during locking in this case is, in fact, smaller than with a sinusoidal a-c of 300 mc. Figure 14 shows that diode II is turned back before it reaches its peak. Figure 15 shows that the output pulse has a smaller and delayed flat-top region compared to that of the pulse obtained with a sinusoidal drive. Although harmonics in the a-c source definitely help to make the locking process successful, they introduce the practical problem of distributing the composite a-c waveform with precise shape, balance, and level. The tolerance requirements on this waveform and on the d-c bias are very stringent, since it is required that the slowly varying part of the waveform occur during the very short locking interval.

The factor  $\bar{v}_D - R \bar{i}_D$  in Equation (25) is the only factor which depends on the shape of the tunnel-diode characteristic. It is the voltage

Fig. 14—Incident waves on the diodes in the 10-ma circuit operating with a 1000-mc nonsinusoidal source.

Fig. 15—Output pulse of the 10-ma circuit operating with a 1000 mc nonsinusoidal source.

### ANALYSIS OF THE EFFECTS OF REACTANCES

departure of the point  $\bar{v}_{p}$ ,  $\bar{i}_{p}$  (which is on the negative-resistance region part of the characteristic) from the linear part of the lowvoltage positive-resistance region. It is thus a measure of the width of the peak. The point  $\bar{v}_D$ ,  $\bar{\iota}_D$ , which is close to the point to which diode II may go, is fairly independent of other circuit parameters, and consequently the peak-width factor  $\bar{v}_p - R \bar{\iota}_p$  is also fairly independent of the circuit parameters, including the peak current. For the characteristic shown in Figure 2, the peak-width factor varies between 40 and 60 millivolts. The peak width has a significant influence on the locking process. Suppose, for example, that it is zero, which it would be if the characteristic abruptly changed from a positive resistance Rto a negative resistance. Then, the maximum frequency would be entirely dependent on the logic input. For the 10-milliampere circuit, the maximum frequency would be only 60 mc! If the peaks are broad, the diodes have more time to "talk" to each other before something drastic happens. One way of obtaining something equivalent to broad peaks, is to drive the circuit "backwards," i.e., to let the process start with both diodes in their high state and let them lock over their broad valley regions. This mode of operation has several disadvantagesit is very difficult to manufacture tunnel diodes with tight tolerances on their properties in the valley- and high-voltage regions; these regions are temperature and pressure sensitive; the capacitance in these regions can be much larger than at the peaks; and the power consumption of the circuit is very high.

For a circuit operating in the ordinary mode with a sinusoidal drive of sufficient amplitude to produce flat-top output pulses

$$\bar{v}_D - R \bar{i}_D \simeq 50 \text{ mv}, \quad \frac{dE(\vartheta)}{d\vartheta} \bigg|_{t=t_0} \simeq 200 \text{ mv},$$

and consequently, the critical frequency is

$$f_{\rm crit} \simeq \frac{1}{8\pi} \frac{1}{\tau} \frac{(R+r)(Z-r)}{\left(1+\frac{R}{Z}\right)^2 Z(Z+r)}.$$

(27)

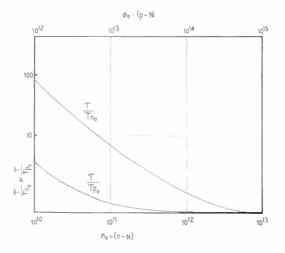

The parameters R,  $Z = \sqrt{L/C}$  and  $\tau = \sqrt{LC}$  are functions of the peak current. For diodes made of the same material, the resistance R varies with peak current as  $R = k_R/I_p$ . To conform with the characteristic shown in Figure 2, we shall assume that  $k_R = 35$  millivolts. The diode capacitance at peak voltage varies with peak current according to the

relationship  $C = K_c I_p + C''$ . Usually the diode capacitance is specified at valley voltage. According to Equation (4), the valley capacitance is approximately  $C_v = 1.6 K_c I_p + C''$ .

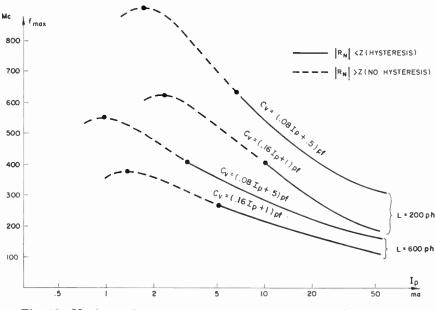

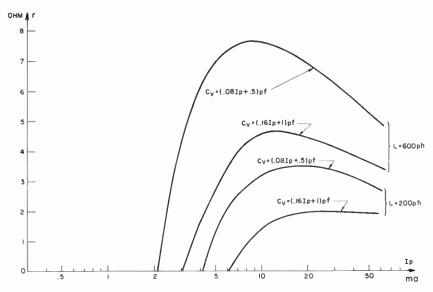

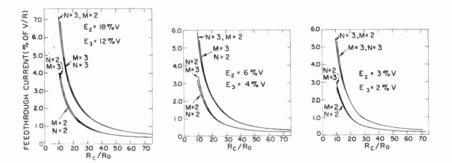

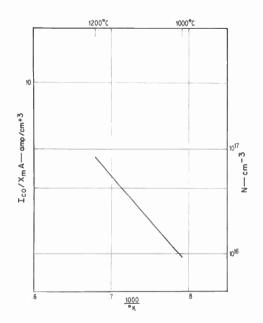

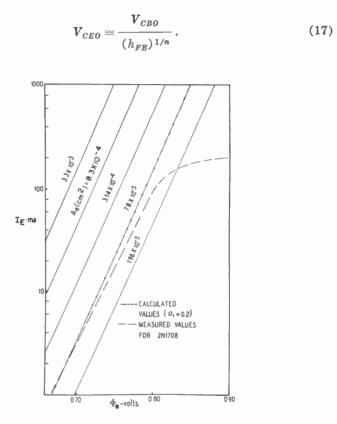

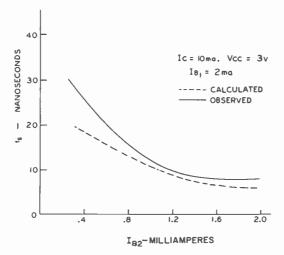

With this dependence of R and C on peak current, the critical frequency can be determined as a function of peak current for an optimum source resistance r. This relation is shown in Figure 16 for two cases of inductances, L = 600 ph and L = 200 ph, and for two cases of diode capacitances,  $C_v = .16I_p + 1$  pf and  $C_v = .08I_p + .5$  pf, where  $I_p$  is in milliamperes. Figure 17 shows the optimum source resistance as a function of peak current. Figure 16 shows that the critical frequency

Fig. 16—Maximum frequency versus peak current for optimum source resistance and small input signals.

has a maximum for a rather small peak current. The optimum peak current is roughly  $k_R/\sqrt{L/C''}$ . The optimum peak current is below 10 milliamperes even for extremely small inductances (L = 100 ph), extremely large case capacitances (C'' = 5 pf), and extremely large peak voltages  $(V_p = 100 \text{ mv}, k_R = 50 \text{ mv})$ . The optimum source resistance for an optimum peak current is always zero, and for a wide range of peak currents and reactances it is below 10 ohms.

Diodes with peak currents in the vicinity of this optimum peak current have case capacitances which are substantially larger than their junction capacitances. Consequently  $Z = \sqrt{L/C''}$  and R = Z. Since

the magnitude of the negative resistance in the steepest part of the negative-resistance region is approximately  $R_n \approx 3R \approx 3Z$ , the maximum reflection gain of an optimum peak current diode is approximately

$$\left(\frac{d\theta\left(C\right)}{dC}\right)_{\max} = \frac{R_{n}+Z}{R_{n}-Z} \simeq 2.$$

With such a small gain, the locking process must, in general, span a duration much longer than  $4\tau$ , which violates the assumptions on which Equation (25) is based. The validity of Equation (25) and of the curves in Figure 15 are therefore doubtful in the vicinity of the optimum peak current. The performance of circuits with low-gain

Fig. 17—Optimum source resistance for high locking frequency versus peak current.

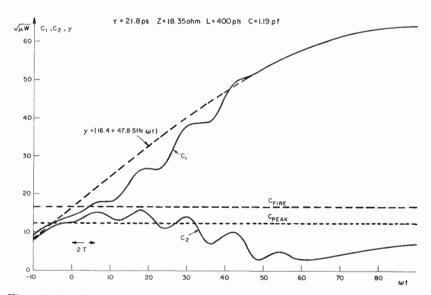

diodes must therefore be analyzed with a point-by-point determination of the sequence of events. Consider, for example, a circuit with optimum peak current diodes, zero source resistance, and no load. Let the peak current be  $I_p = 1.91$  milliamperes, the capacitance  $C = .1I_p + 1$ = 1.19 pf, the inductance L = 400 ph, and the logic input current  $2\Delta i$  $= .1I_p$ . The delay is  $\tau = 21.8$  ps and the characteristic impedance is Z = R = 18.35 ohms. Figure 18 shows the incident waves on the diodes as a function of time when the circuit operates at 380 mc. It is seen that the locking process, although successful, spans a long duration of

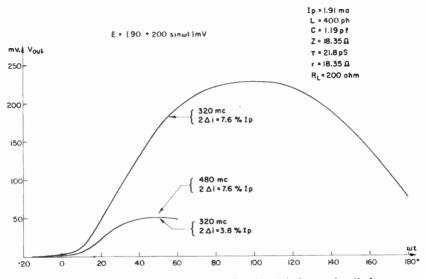

time during which diode II makes several excursions deep into the negative-resistance region ( $C_{\rm fire}$  in Figure 18 corresponds to the steepest part of the negative-resistance region). This oscillatory behavio is typical for circuits with small source resistors. Besides being unreliable, this circuit is unrealizable (r = 0) and useless ( $R_L = \infty$ ). When the circuit operates with a realistic source resistance r = 18.35 ohms and a load  $R_L = 200$  ohms, the output pulse is as shown in Figure 19. The circuit can operate at 320 mc with an input current  $2\Delta i = 0.076 I_p$ , but does not work if either the frequency is increased to 480 mc or the logic input is reduced to  $0.038I_p$ . The rise time is long, the pulse top rounded, and the success of the locking process is sensitively de-

Fig. 18—Incident waves on diodes in a circuit with 1.9-ma diodes, no source resistance, and no load operating with a 380-mc sinusoidal source.

pendent of the logic input. According to Equation (25), the critical frequency for this circuit is zero and the maximum frequency with an input current  $2\Delta i = 0.076I_p$  is only 100 mc, which is much lower than the 320 mc at which the circuit actually can work. Equation (25) is clearly not valid for low-gain diodes. Low-gain diodes are, however, of little interest for high-speed circuits, not only because of poor rise time, strong dependence on logic input, rounded pulses, and sensitivity to the exact shape of the negative resistance region, but also because, for all realistic reactances, the peak current is extremely low with the consequence that the impedance level is impractically high.

# ANALYSIS OF THE EFFECTS OF REACTANCES

For these reasons, a peak current must be chosen which is much larger than the peak current that theoretically gives the highest frequency. Some hysteresis in the reflection characteristic is desirable to secure a fast and reliable locking process and a short rise time. Judging from Figure 15, it appears that for a wide range of realistic reactances, the best compromise is a peak current between 5 and 15 milliamperes. At larger peak currents the impedance level becomes so low that lead inductances limit the speed, while at lower peak currents, the impedance level becomes so high that the diode capacitances limit the rise time. The 10-milliampere circuit is an example of a compromise design. The inductance assumed, L = 400 ph, is perhaps

Fig. 19-Output waveforms of a circuit with low-gain diodes.

optimistically small. In reality the inductance is likely to be larger than 500 ph, and the maximum frequency closer to 250 mc than to 300 mc. Although the optimum source resistance for high-frequency operation is, according to Figure 17, about 3 ohms, a larger source resistance (r = 6.5 ohms) has been chosen to widen the top of the pulse and to prevent oscillations of a type which are discussed in the next section.

The effect of imbalances can be estimated by perturbation methods. During the locking process, imbalances generate signals which have the same effect as a logic input current, and consequently they "eat up" some of the available input. An estimate of these undesirable

signals is not difficult to carry out, but is a rather lengthy procedure and is not included here. The main conclusion is, as can be guessed, that tolerance requirements are extremely stringent when the circuit operates close to its maximum frequency. The balance of the capacitances and the peak widths of the diodes, which can be expressed in terms of peak-voltage balance, is particularly critical. Peak voltages and diode capacitances must be balanced within less than 10 per cent for a worst-case design. However, it is not realistic to hope that a worst-case-designed circuit can operate at the predicted ultimate speed. Individual adjustments of the threshold bias on the gates appear to be a necessity. Imbalances due to aging are probably small compared to initial imbalances.

#### OTHER REACTIVE EFFECTS

#### Recovery

The analysis of the locking process in the previous section is a transient analysis based on the assumption that the circuit has completely recovered from past transients at the beginning of the process. When the locking process starts, both diodes have been in the linear part of their low-voltage positive-resistance regions for about half a cycle of the fundamental frequency of the power source. An investigation of the natural complex frequencies of the circuit, with the diodes replaced by resistances R, reveals that for all realistic reactances and all realistic designs of the circuit, the circuit has recovered within half a cycle of the maximum frequency at which the circuit can operate with a sinusoidal a-c. Thus, in a properly designed circuit, recovery is not a problem. If the frequency is boosted by using harmonics in the a-c waveform, recovery may become a problem. Also, if the inductance in the load is exceptionally large,  $L_L > 10$  nh (nh = nanohenry =  $10^{-9}$  henry), the circuit may not recover. Whatever is left of the output current in  $L_L$  when the process starts anew, acts as a logic input current. This may cause alternate positive and negative locking of the circuit.

When the circuit produces an output of the same sign for a long duration of time, it is possible that a bias can build up, either by thermal imbalance of the diodes or by "d-c buildup" in the powerdistribution system. With some care in the choice of diodes and in the design of the power-distribution system,<sup>3</sup> such bias buildup can be limited to a tolerable level.

#### Self Resetting

Occasionally it is found that the diode which initially switches will

reset itself. This phenomenon may occur even at low source frequencies if the source resistance is small and the lead inductances are large. It can be discussed with the help of the transmission-line model shown in Figure 6. Let diode I be favored by the logic input. Let the locking process be successful, and let diode I switch. A strong wave of intensity A is emitted from diode I at the switching instant t. At an instant  $t + 2\tau$  diode I receives a reflected wave  $S_{11}A$ . If  $S_{11}$  is negative, which it is if  $r(r+2Z_L) < Z^2$ , this reflected wave can be strong enough to reset diode 1. Even if it is not strong enough to reset diode I, it will cause an undesirable oscillatory behavior of the switching process. In a properly designed circuit, the source resistance and the load should be chosen so as to make  $S_{11} > 0$ , i.e.,  $r(r + 2Z_L) > Z^2$ . The 10-milliampere circuit satisfies this condition. Even when  $S_{11} > 0$ , self-resetting may occur. The strong wave A, emitted by diode I, is also transferred through the resistive pad, reaches diode II, drives it deeply back into its low-voltage, positive-resistance region, is reflected by diode II, goes back through the pad, and reaches diode I at an instant  $t+4\tau$ with an intensity  $\psi S_{12}^2 A$ . If  $\psi$  is negative, which it generally is, this wave may be strong enough to reset diode I. To avoid this kind of self-resetting,  $S_{12}$  and  $|\psi|$  must not be too large. This means that the source resistance must not be too small and the peak current must not be too large. An exact criterion for avoiding self-resetting is difficult to derive, because it depends on the shape of the characteristic throughout the negative-resistance region. A sufficient condition is that  $S_{11} + \psi S_{12}^2 > 0$ . The 10-milliampere circuit satisfies this condition when the source resistance is 6.5 ohms, but not when the source resistance is 3 ohms, which is theoretically the optimum for high-frequency operation. The choice of source resistance is thus a compromise between the desire to have low attenuation in the communication path between the diodes to secure locking and high attenuation to prevent self-resetting. After self-resetting a new and usually unsuccessful locking process starts. Self-resetting may also repeat a few times.

Self-resetting occurs more readily at low frequencies than at high frequencies. At high frequencies the source may drive diode I so far into its high-voltage positive-resistance region before the reflected wave comes back, that the reflected wave cannot reset the diode. Thus, it is possible that a circuit may work at high frequencies but not at low frequencies.

# Switching Speed

In the transmission-line model, diodes with hysteresis switch infinitely fast. This is an obvious misrepresentation of reality. If all

of distributing the composite a-c waveform with precise balance, shape, and level. It appears to be difficult to use such a composite a-c clocksource in a practical system.

The repetition rate can also be significantly increased at the expense of the shape and amplitude of the output pulse by operating the circuit with a sinusoidal a-c of less than "nominal" amplitude. This conclusion is confirmed by the experimental fact that balanced-pair circuits have operated up to 1200 mc.<sup>3</sup> However, tolerance requirements on components and sources are already very stringent in a system operating with "nominal" a-c amplitude.<sup>3</sup> By reducing the a-c amplitude and degrading the pulse shape, the tolerance requirements become impractical. Thus, it does not appear that the method of increasing the repetition rate by reducing the amplitude of the a-c could be used in a practical system.

The reactances have their most significant influence on the performance of the circuit during the locking process, which occurs during the small fraction of the a-c cycle when the diodes are driven over their peaks. Their effects during the remaining part of the a-c cycle have, in general, a minor influence on the performance of the circuit. Reactive effects such as ringing, recovery, oscillations, limited switching speed, thermal unbalance and d-c buildup during repetitious switching can be kept under control with some care in the design of the circuit, the interconnections between circuits, and the power distribution system.

Attempts to optimize the parameters of the balanced-pair circuit indicate that for a wide range of realistic reactances the optimum peak current is between 5 and 15 milliamperes. At higher peak currents, the impedance level of the circuit is so low that lead inductances limit the speed, while at lower peak currents the diode capacitances limit the speed. This result, which indicates that a maximum speed is obtained at an impedance level that represents a compromise between the speed-limiting effects of capacitances and inductances in devices, components, and interconnections, may be of interest for the design of high-speed circuits and systems in general.

# AN EVALUATION OF TUNNEL-DIODE BALANCED-PAIR LOGIC SYSTEMS

#### By

### H. S. MIILLER AND R. A. POWLUS

#### RCA Laboratories Princeton, N. J.

Summary—The major problems that thus far have limited applications of tunnel-diode circuits in computers are those of distribution of power supply voltages, packaging, subsystem fabrication techniques, and system tolerances. This paper presents experimental and analytical results obtained in an exploratory program to determine, in relation to the above problems, the applicability of tunnel-diode balanced-pair circuits as building blocks for high-speed computers.

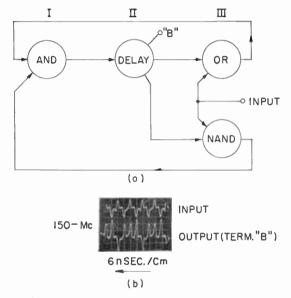

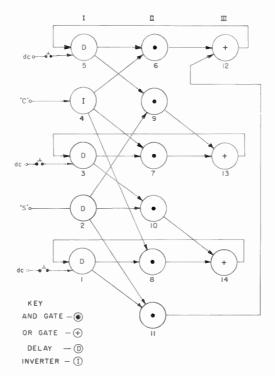

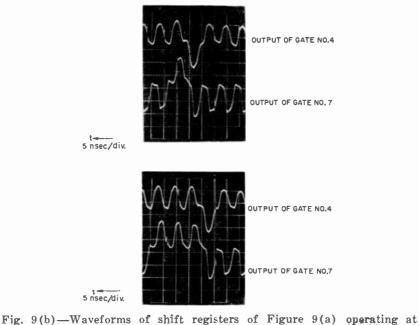

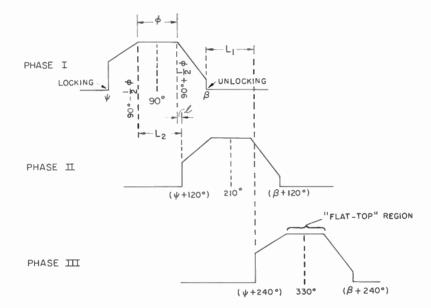

Part I discusses solutions to the first three of the above problems and presents experimental results obtained from operating balanced-pair circuits with sinusoidal power supplies having a frequency (repetition rate) range of 100 mc to 1 kmc. These power supplies have, in addition to the a-c component, a d-c component which is used for biasing purposes. Two basic power distribution techniques are described. These techniques were employed in scale-of-two counters operating at both 150- and 450-mc repetition rates and in two, three-bit end-around shift registers operating at 150-mc repetition rates. The fabrication technique used in one of the shift registers, which is suitable for small systems, is also described.

Part II deals with the problem of system tolerances, which remains as the limiting factor in the application of tunnel-diode balanced-pair circuits for high-speed computers.

# PART I—POWER SUPPLY, PACKAGING AND SUBSYSTEM FABRICATION

### INTRODUCTION

UNNEL-DIODES are being considered as prime candidates for high-speed computer applications due to their high cutoff frequency, simplicity, and stability.<sup>1-5</sup> The major problems which have thus far limited applications of tunnel-diode circuits in

<sup>&</sup>lt;sup>1</sup> L. Esaki, "New Phenomenon in Narrow Germanium p-n Junctions," *Phys. Rev.*, Vol. 109, p. 603, January 15, 1958.

<sup>&</sup>lt;sup>2</sup> H. S. Sommers, "Tunnel Diodes as High-Frequency Devices," *Proc. I.R.E.*, Vol. 47, p. 1201, July, 1959.

<sup>&</sup>lt;sup>8</sup> R. Trambarulo and C. A. Burns, "Esaki Diode Oscillators from 3 to 40 kmc," *Proc. I.R.E.*, Vol. 48, p. 1776, October, 1960.

<sup>&</sup>lt;sup>4</sup> M. H. Lewin, "Negative Resistance Elements as Digital Computer Components," *Proc. E.J.C.C.*, Boston Mass., p. 15, December 1-3, 1959.

<sup>&</sup>lt;sup>5</sup> J. A. Rajchman. "Solid-State Microwave High-Speed Computers," Proc. E.J.C.C., Boston, Mass., p. 38, December 1-3, 1959.

computers are those of distribution of power supply voltages, packaging, subsystem fabrication techniques, and system tolerances. The purpose of this paper is to report results obtained in an exploratory program to determine, in relation to the above system problems, the applicability of a particular class of tunnel-diode circuits, the balancedpair circuits, as building blocks for high-speed computers.

A logical building block must provide a functionally complete set as well as meet electrical requirements of signal amplification and standardization. As logical decision rates (the reciprocal of the time required to perform a logical decision) increase, building-block requirements, particularly those of physical size and reliability, vastly increase. Geometrical positioning and logical versatility of high-speed (0.5-nanosecond stage delay) computer building blocks are extremely important since the delay in a wiring path four inches long is equivalent to one stage delay. Due to these constraints, system organization is no longer separable from geometrical problems.

Tunnel-diode balanced-pair circuits amplify and standardize signals each time a logical decision is made, and are, in principle, capable of 11 separate logical functions in addition to amplification. They are of small size  $(3 \times 10^{-2} \text{ cubic inch})$  and low in power consumption (on the order of 50 milliwatts). These properties qualify balanced-pair circuits for consideration as high-speed computer building blocks.

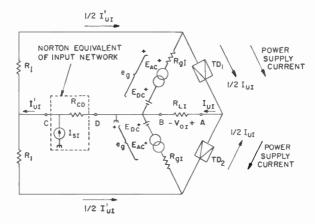

A balanced-pair circuit is basically a pair of matched tunnel-diodes and matched power supplies arranged in a symmetrical configuration giving a one-port circuit which is capable of both positive and negative output pulses. Logical directivity is obtained by using a multiphase power supply system. A balanced-pair majority circuit<sup>6</sup> uses two opposite nodes of the symmetric circuit, one of which is common to the two power supplies and the other of which is common to the two tunnel diodes, as input-output terminals. A balanced-pair inverter circuit<sup>7</sup> uses as output terminals the same input-output terminals as the majority circuit. One of the inverter input terminals, which is also an output terminal, is the node common to the two power supplies. The other input terminal is the intersection of two resistors connected in series between the two remaining nodes of the symmetric circuit. Each of these two nodes is common to a power supply and a tunnel diode.

Part I of this two-part paper discusses basic concepts of the two types of balanced-pair circuits, namely, operating principles of both

<sup>&</sup>lt;sup>6</sup> A. W. Lo. French patent No. 1.246,094 issued January 27, 1960; Belgian patent No. 586,900 issued January 25, 1960.

<sup>&</sup>lt;sup>7</sup> Interm Research Report No. 7A for High-Speed Data Processor System Research, RCA, Camden. N. J., for the period June 1, 1960 to August 30, 1960, p. 2-2 to 2-4. ASTIA document No. AD 253,919 (11 April 1961).

majority and inverter balanced-pair circuits. Each of these concepts is viewed from purely static conditions. That is, all reactances are neglected and switching is considered to be instantaneous. In addition, Part I describes methods of distributing a-c power-supply voltages to large numbers of balanced-pair circuits, several small experimental subsystems which were constructed to evaluate balanced-pair circuits, circuit packaging, and subsystem fabrication techniques useful for large-scale subsystems. Although fabrication techniques discussed were not evaluated above 450 mc, the concepts employed appear to be extendable to 1-kmc systems.

A discussion of the factors which govern the widths of output pulses of majority circuits, the restrictions on lengths of transmission lines used for logic interconnections between balanced-pair circuits, and of the influence of these factors on the problem of circuit tolerances is contained in Part II. The results of a static tolerance analysis of balanced-pair logic systems are also presented.

# MAJORITY CIRCUIT

Majority logic is performed with a linear summation network at the input-output terminals of a majority circuit. Majority circuits discriminate between positive and negative current inputs resulting from the summation, then amplify and produce standardized output pulses. Tolerances permitting, weighted majority logic is possible. The logical AND and OR operations are special cases of the majority operation with a constant reference, either "1" or "0", applied to one or more inputs of the summation network. The effect of this constant reference can be achieved by either initially choosing tunnel diodes with unequal peak or valley currents or unbalancing two matched diodes with a d-c current source applied directly to the input-output terminals.

Principles governing operation of majority circuits will now be described in terms of operating points on tunnel-diode voltage-current characteristics. All reactances are neglected and switching is considered instantaneous.

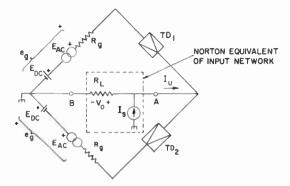

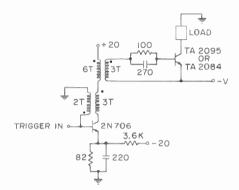

The schematic diagram of a balanced-pair majority circuit is shown in Figure 1. The two matched power supplies,  $e_g$ , each having a sinusoidal waveform with a d-c component, can be varied to give two modes of operation which differ with respect to one another due to relative magnitudes of the d-c component of the power supplies. In mode (a), the d-c component is such that both tunnel diodes are initially in the low-voltage state. with one tunnel diode switching to its high-voltage state: in mode (b), both tunnel diodes are initially held in their highvoltage state by the d-c component of the power supplies, with one

Fig. 1—Tunnel-diode balanced-pair majority circuit.  $I_{\epsilon}$  is the Norton equivalent of the input current from other circuits.

tunnel diode switching to its low-voltage state. It will be shown that mode (a) operation is preferable. But first a more complete description of the two modes of operation will be given.

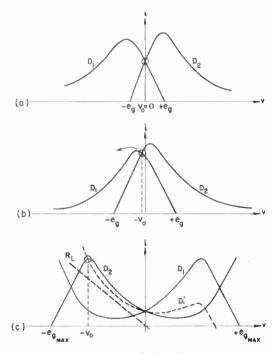

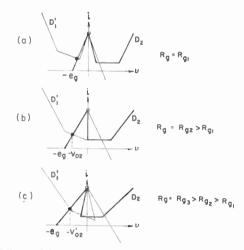

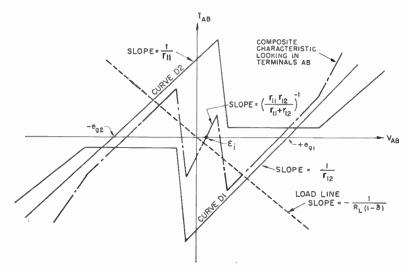

The basic operation of a majority circuit in mode (a) is illustrated in Figure 2. Here, curve  $D_1$ , which represents the V-I characteristic

Fig. 2—Characteristic curves of a majority circuit for various values of  $e_{p}$  in mode (a) operation.

of diode  $TD_1$ . is a nonlinear load line applied to curve  $D_2$ , which represents the V-I characteristic of diode  $TD_2$ . (Effects of the source resistance of the power supplies,  $R_g$ , is included in the curves  $D_1$  and  $D_2$ .) Initially, both tunnel diodes are in their low-voltage regions as shown in Figure 2a and the output voltage,  $V_0$ , is zero. As the balanced power supply voltages,  $e_g$ , increase, as shown in Figure 2b,  $V_0$  will assume a negative value if the peak current of diode  $TD_2$ ,  $I_{P2}$ , is greater than the peak current of diode  $TD_1$ ,  $I_{P1}$ . Conversely, if  $I_{P1}$  is greater than  $I_{P2}$ ,  $V_0$  will be positive.\* When  $e_g$  reaches its maximum

Fig. 3—Characteristic curves of a majority circuit for various values of  $e_g$  in mode (b) operation.

value, the characteristic curves are shown in Figure 2c. Effects of a net load,  $R_L$ , i.e., the parallel combination of fan-in and fan-out resistors, across input-output terminals AB in Figure 1, may be included as an increase in the loading on diode TD<sub>2</sub>. The net load line on curve D<sub>2</sub> is then a composite of D<sub>1</sub> and  $R_L$ , D'<sub>1</sub> in Figure 2c.

Operation of a majority circuit in mode (b) is illustrated in Figure 3. Here, curve  $D_2$  is a nonlinear load line applied to curve  $D_1$ . Initially,

<sup>\*</sup> In this paper, a positive  $V_o$  represents a "1" and a negative  $V_o$  represents a "0."

both tunnel diodes are in their high-voltage regions and  $V_0$  is zero as shown in Figure 3a. As  $e_g$  decreases (Figure 3b),  $V_0$  assumes a positive value if the valley current of diode TD<sub>1</sub>,  $I_{V1}$ , is greater than the valley current of diode TD<sub>2</sub>,  $I_{V2}$ . Conversely, if  $I_{V2}$  is greater than  $I_{V1}$ ,  $V_0$ will be negative. When  $e_g$  reaches its minimum value, the characteristic curves are as shown in Figure 3c.

Majority circuits exhibit a locking property,<sup>5.6</sup> i.e., circuit states which represent a "1" and "0" at the output terminals AB are, once they have been reached, stable and independent of other inputs and reasonable loading. For a unilateral logic system, then, it is sufficient that majority circuits, when bilaterally coupled, be powered with a multiphase power supply of at least three phases.

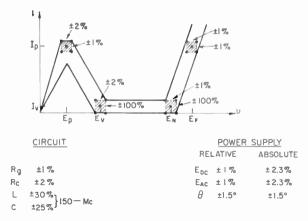

When a majority circuit is operated in mode (a), neglecting reactances, the instant of locking, or the point where the state which the circuit will enter is determined, is when  $e_g = V_P$ , where  $V_P$  is equal to the peak voltage,  $E_P$ , associated with the tunnel-diode characteristic plus  $I_P R_g$ , the voltage drop across  $R_g$ . For mode (b), locking takes place when  $e_g = V_V$ , where  $V_V$  is equal to the valley voltage,  $E_v$ , associated with the tunnel-diode characteristics plus  $I_V R_g$ , the voltage drop across  $R_g$ . Experience has shown that  $E_V$  has a greater variation from circuit to circuit than  $E_p$ . This indicates that a switching threshold as determined by the valley region of a tunnel-diode characteristic is not clearly defined. For this reason, mode (a) operation is preferable.

Unbalancing the tunnel-diode currents as their peaks or valleys are being passed determines the ultimate circuit *state*. This imbalance can be accomplished by inserting a small current into terminal A if diode  $TD_2$  is to enter its high-voltage region, or by drawing a small current from terminal A if diode  $TD_1$  is to enter its high-voltage region (see Figure 1). Final circuit *states* also can be affected by choosing tunnel diodes with unbalanced peak or valley currents. As such, majority circuits not only discriminate as to the polarity of the input current from the linear summation network but also the magnitude of these current inputs.

The magnitude of the ratio of current entering or leaving terminal A (Figure 1) to nominal peak current of the tunnel diodes for an operating circuit is termed the *sensitivity* of a majority circuit. *Minimum sensitivity* denotes the lowest value of sensitivity for which a circuit will operate properly. Experimentally, minimum sensitivities of the order of 1 per cent were commonly achieved at a 150-mc repetition rate by adjusting only the d-c bias current. This adjustment served to overcome many inherent circuit imbalances. Similar experiments have required a minimum sensitivity of 6 per cent for operation at 1-kmc and 1.2-kmc repetition rates. Empirical information on output-

| Frequency<br>(mc) | Peak Current of<br>Tunnel Diode<br>(ma) | Net<br>Ohms | Load<br>Current<br>(ma) | Minimum<br>Sensitivity<br>(%) | Output<br>Voltage<br>(mv) |

|-------------------|-----------------------------------------|-------------|-------------------------|-------------------------------|---------------------------|

| 150               | 5                                       | 7.5         | 2.4                     | 1                             | ±180                      |

| 150               | 50                                      | 12.5        | 14                      | 1.5                           | $\pm 180$                 |

| 750               | 50                                      | 25          | 7.2                     | 6                             | $\pm 180$                 |

| 1200              | 50                                      | 50          | 3.6                     | 6                             | $\pm 180*$                |

Table I

\* estimate

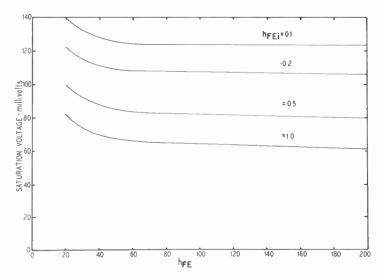

voltage amplitude, maximum loading, and sensitivity is sufficient to give a circuit's fan power and yield an appropriate value for coupling resistors. Values of minimum sensitivity, output-voltage amplitude, and net load derived from operation of several majority circuits in the 150-mc to 1.2-kmc frequency range, are tabulated in Table I. Typical V-I characteristics of the germanium tunnel diodes used to obtain the results given in Table I are shown in Figure 4. The capacitances of the 50-ma and 5-ma diodes were 10 picofarads ( $10 \times 10^{-12}$  farad) and 3 picofarads, respectively.

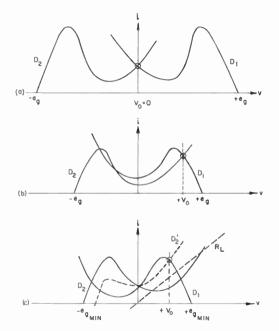

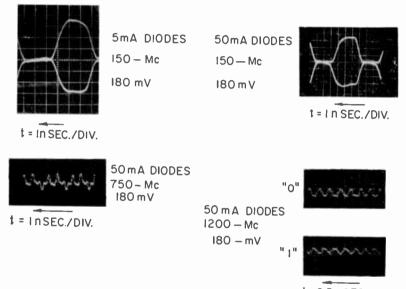

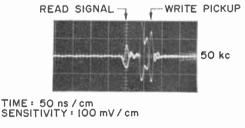

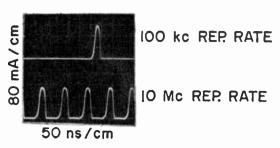

Figure 5 shows typical "1" and "0" output waveforms of the 5-ma and 50-ma majority circuits operating at a 150-mc repetition rate.

Fig. 4—Typical tunnel-diode volt-ampere characteristics: (a) 50-ma germanium unit; (b) 5-ma germanium unit.

In addition, Figure 5 shows an output voltage waveform for 1.2-kmc operation.<sup>\*</sup> Measured rise and fall times were 0.3 nanosecond ( $0.3 \times 10^{-9}$  second) which was equal to the rise time of the sampling oscilloscope. The triangular shape of the output pulses is typical of the performance of these majority circuits above 150 mc.

If the information given in Table I is used to calculate fan-power, the 5- and 50-ma circuits at 150 mc have fan-powers of 48 and 14, respectively, while the 50-ma circuits at 750-mc and 1,200-mc have

t = 0.5 n SEC./DIV.

Fig. 5-Output waveforms of balanced-pair majority circuits.

fan-powers of two and one, respectively. The information used to calculate these values of fan power was obtained from circuits operating individually with no concern for system tolerances. When these circuits are incorporated into a system, various tolerances must be considered. In order to obtain reliable operation, much of this fanpower must be sacrificed. Thus, even though majority circuits can operate in excess of 1-kmc repetition rates, the amount of fan-power available at repetition rates above the 150-mc range is insufficient to allow any sacrifice for reasonable system tolerances.

The exact amount of fan-power as a function of system tolerances for the 5- and 50-ma circuits at 150 mc is discussed in Part II.

<sup>&</sup>lt;sup>e</sup> Unless otherwise specified, mode (a) operation was used in experimental work described in this paper.

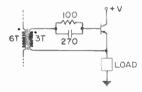

#### INVERTER CIRCUIT

The balanced-pair inverter circuit is shown in Figure 6. An input or signal current,  $I_{UI}'$ , at inversion terminals CD will produce equal signal currents in resistors labeled  $R_1$  in the figure. If the net output resistance,  $R_{LI}$ , across terminals AB is infinite, no signal current flows through the two diodes. If  $R_{LI}$  is finite, an additional path to ground is provided for input signal currents. As a consequence, one half of  $I_{UI}$ , the current through  $R_{LI}$ , flows through each of the tunnel-diodes,  $TD_1$  and  $TD_2$ . In combination with power-supply currents, this results in unequal currents in the diodes. The tunnel-diode with a larger net

Fig. 6—Balanced-pair inverter circuit. Terminals CD are the inversion input terminals and terminals AB are the output terminals.  $I_{st}$  is the Norton equivalent input current from other circuits.

current (in this case  $TD_1$ ) will be switched to its high-voltage region. Thus, a current entering terminal C will cause diode  $TD_1$  to be switched to its high-voltage region with a resulting negative output voltage,  $V_{OI}$ , across  $R_{LI}$ . Conversely, a current leaving terminal C will cause diode  $TD_2$  to be switched to its high-voltage region with a resulting positive output voltage,  $V_{OI}$ , across  $R_{LI}$ .

It is possible to perform majority logic with some inputs complemented by using the inverter circuit. Input signals are connected to both its input and output terminals (complemented inputs to terminals CD). Thus, balanced-pair majority and inverter circuits are capable of 11 separate logical junctions including amplification.<sup>7</sup> In other respects, balanced-pair inverter circuits are similar in behavior to majority circuits; thus. further discussions are restricted primarily to majority circuits.

Two balanced-pair building blocks, one which is capable of AND and OR logic and another which is capable of inversion, have been described. Together, these building blocks provide a functionally complete set that amplifies and standardizes logic signals. The problems of distributing the high-frequency a-c supply voltages as well as problems of packaging and subsystem fabrication techniques are determining factors in successful integration of these building blocks into highspeed computers. Solutions to these problems will now be discussed.

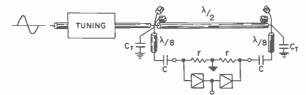

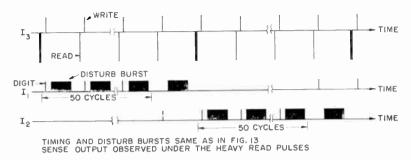

### **POWER-SUPPLY REQUIREMENTS**